AN-13-0014

作者: Shuo Zhang, Runsheng Zhou

### 摘要

上篇应用手册<sup>[1]</sup>介绍了芯片级ESD和系统级ESD的多方面差异,并阐明了芯片级ESD与IEC-61000标准下的系统级ESD没有直接联系和替代性。相比于系统级ESD和客户终端应用密切相关,芯片级ESD和Latch up测试旨在评估芯片本身对静电放电和闩锁效应的敏感性和抗扰度。本文介绍了芯片出厂前HBM、CDM和Latch up的测试原理和国际通用标准规范,并总结分析了JEDEC标准和AEC-Q100标准的主要差异。

### 目录

| 1. 芯片级ESD/Latch up测试简介                                         | 2 |

|----------------------------------------------------------------|---|

| 1.1. 芯片级ESD测试                                                  | 2 |

| 1.2. Latch up测试                                                | 2 |

| 2. HBM/CDM/Latch up标准差异分析 ···································· | 3 |

| 2.1. HBM测试标准及差异 ····································           | 3 |

| 2.2. CDM测试标准及差异                                                | 5 |

| 2.3. Latch up测试标准及差异                                           | 6 |

| 3. 总结                                                          | 8 |

| 4. 修订历史                                                        | 9 |

### 1.芯片级ESD/Latch up测试简介

芯片级ESD和Latch up测试是芯片出厂前评估芯片抗静电放电和抗闩锁能力的重要评估方法,针对ESD和Latch up所设计的保护结构通常占据较大的版图面积,从而确保芯片能够达到相应的ESD和Latch up等级,在生产、制造、运输和应用过程中可靠工作。

#### 1.1.芯片级ESD测试

芯片级ESD分为HBM(Human-Body Model)、CDM(Charged-Device Model)和MM(Machine-Model),分别用于模拟人体带电对芯片放电、芯片自身带电对外放电和机器带电对芯片放电三种情形。然而,由于MM试验可重复性差、筛选效率低等原因,已被业界证明可以由HBM和CDM实现覆盖,JEP172A标准中对此有详细说明,AEC-Q100随后也将MM模型废止。因此,本文仅介绍HBM和CDM的相关测试标准及差异,MM不再赘述。

#### 1.2.Latch up测试

闩锁效应(Latch-Up)是指在电源引脚与接地端之间形成低阻抗通路的一种状态。该状态由触发信号(电流注入或过电压)引发,一旦激活,即便触发信号消失,低阻抗通路仍会持续存在。这种低阻抗通路可能因电流过大导致系统异常或芯片永久性损坏。在 CMOS 集成电路的设计中,构成 NMOS 和 PMOS 晶体管的 PN 结彼此靠近,会不可避免地形成寄生晶体管和寄生二极管。这些寄生结构会组成 PNPN 晶闸管(SCR)。当电压或电流超出正常工作范围时,可能触发 SCR,进而引发闩锁效应。

Latch up测试通过两种测试类型对芯片内部器件的闩锁敏感结构进行测试:

1)电源引脚过压测试,通过在电源对地之间施加最大电压实现,该电压为1.5倍电源工作电压和最大应力电压(Maximum stress voltage,MSV)中的较小值。其中,MSV指的是在Latch up测试期间,施加于任意引脚且不会导致器件因与Latch up无关的电过应力EOS(Electrical over-stress,过电应力)最大允许电压,MSV仅适用于Latch up测试中,用于保护被测器件免受与Latch up 无关的应力而造成损坏。MSV值需要考虑工艺技术和电路结构拓扑,对于使用低压器件的模拟芯片而言,芯片由于EOS而发生破坏的MSV通常大于1.5倍工作电压。

2)信号引脚电流注入测试,通过电压依从限制的电流施加(I-Test)或电流依从限制的电压施加(E-Test)实现;使用I-Test方法时注入电流≥100mA,使用E-Test方法时为最大限压下电流值;

### 2.HBM/CDM/Latch up标准差异分析

#### 2.1.HBM测试标准及差异

HBM国际通用标准为ANSI/ESDA/JEDEC JS-001-2023(以下简称JS-001)和AEC-Q100-002-REVE。其中,JS-001为ANSI(美国国家标准学会)、ESDA(美国静电放电协会)和JEDEC(固态技术协会)联合制定的通用HBM测试标准,替代了JESD22-A114-F和ANSI/ESD STM5.1;AEC-Q100-002为汽车电子协会基于JS-001制定的考虑汽车环境适应性的HBM标准。JS-001和AEC-Q100-002标准的主要差异如下表所示:

| 对比项 JS-001                   |                       | AEC-Q100-002                                                         |

|------------------------------|-----------------------|----------------------------------------------------------------------|

| 电压等级                         | <br>                  | 强制从500V开始逐级测试(500V→<br>1000V→2000V),不可跳电压等级测<br>试,若失败需降级至250V/125V测试 |

| 样品引脚分组 允许使用简化引脚组合,即JS-001表2A |                       | 初始测试使用JS-001表2B(全引脚组<br>合),若Fail可允许使用表2A                             |

| Zap次数(单极性)                   | ·<br>· 至少1次/电压等级和引脚组合 | 3次/电压等级和引脚组合                                                         |

| Zap间隔                        | ≥0.1s                 | 沿用JS-001标准(通常≥0.5s)                                                  |

表2.1 JS-001和AEC-Q100-002主要差异对比

从上表可以看出,AEC-Q100-002规定初始测试电压必须为500V,并依次从低电压步进到高电压,避免了测试可能会出现的"窗口效应",即避免由于特定ESD结构可能存在低电压等级Fail而高电压等级Pass的情况,增强了筛选HBM等级的严格性。同时,从低电压步进至高电压的测试方式增加了对ESD器件累积失效的验证。

此外,AEC-Q100-002在引脚组合上的要求也更为严格。在JS-001中定义了两个不同的应力组合表,可根据实际情况选择引脚组合,如表2.2和表2.3所示。其中,表2A允许只对引脚组别内的非供电引脚施加应力,而不需要和其他引脚组别的非供电引脚——测试,以减少测试组合;表2B则规定必须遵循引脚的完整组合原则,即按照电源、接地、IO所有引脚信息,逐个PIN进行测试。在AEC-Q100-002标准中,补充要求初始必须使用表2B进行测试,在使用低寄生测试仪或判定因引脚完整组合测试导致芯片累积失效情况下,可使用表2A。

在Zap次数的要求上,AEC-Q100-002要求每个电压极性进行3次应力施加,相对于JS-001规定的至少1次 Zap要求更为严格,提高了测试结果的可重复性。在Zap间隔的要求上,AEC-Q100-002-REVD中规定两次 放电间隔大于等于0.5秒,而在随后更新的AEC-Q100-002-REVE中未明确规定Zap间隔,此项要求与 JS-001逐渐趋于一致。

总之,JS-001与AEC-Q100-002中对HBM的测试方法和规范非常相似,但AEC-Q100-002针对汽车资格认证增加了额外的要求。随着在Zap间隔要求上两个标准规范之间的差异逐渐收敛,当产品满足AEC-Q100-002对HBM资格的要求时,该产品将足以满足JEDEC/ESDA对HBM资格的要求。

表2.2 JS-001引脚分组表2A

| 引脚组别 | 连接端子B(接地)的引脚      | 连接端子A的引脚       |

|------|-------------------|----------------|

| 1    | (<br> <br>  供电引脚1 | 除供电引脚1外的其他供电引脚 |

| 1    | 1 洪电分解工 一         | 与供电引脚1同组的非供电引脚 |

|      | ···               |                |

| N    |                   | 除供电引脚N外的其他供电引脚 |

| N i  | 供电引脚N             | 与供电引脚N同组的非供电引脚 |

| N+1  | <br>  耦合非供电引脚<br> | 另一耦合非供电引脚      |

#### 表2.3 JS-001引脚分组表2B

| 引脚组别 | 连接端子B(接地)的引脚    | 连接端子A的引脚         |

|------|-----------------|------------------|

| 1    | 供电引脚1           | 除供电引脚1外的其他供电引脚   |

| 1    |                 | 所有非供电引脚          |

|      |                 |                  |

| N    | /+              | 除供电引脚N外的其他供电引脚   |

| N    | 供电引脚N           | 所有非供电引脚          |

| N+1  | 所有非供电引脚(除了被测引脚) | 其他所有非供电引脚(即被测引脚) |

#### 2.2.CDM测试标准及差异

CDM国际通用标准为ANSI/ESDA/JEDEC JS-002-2022(以下简称JS-002)和AEC-Q100-011-REVD。两者的主要差异如下表所示:

表2.4 JS-002和AEC-Q100-011主要差异对比

| 对比项        | 对比项 JS-002 AEC-Q100-011 |                                            |  |

|------------|-------------------------|--------------------------------------------|--|

| 电压等级       | 分阶段升压测试                 | 按电压等级顺序测试,对带有边角封装的<br>Corner Pin进行更高电压等级测试 |  |

| 器件认证等级     | C2a: 500V               | C2a: 500V (Corner pins 750V)               |  |

| 样品测试处理     | 常温前后电性测试,高温可选           | 测试前和测试后进行常温&高温(125°C)测试                    |  |

| Zap次数(单极性) | 至少1次/电压等级和引脚组合          | 3次/电压等级和引脚组合                               |  |

从上表可以看出,在测试电压等级的要求上,AEC-Q100-011要求强制按照电压等级顺序升压测试,且对于DIP\SOIC\QFP\PLCC等封装中含有的Corner Pin进行更高电压等级的测试,对容易放电失效的Corner pin增强了测试要求,这使得JS-002和AEC-Q100-011的验收认证等级也有所不同,如表2.5和表2.6所示,为满足750V角引脚要求,AEC在认证等级分类中插入了额外的级别,并使用TC前缀命名测试电压等级。

表2.5 JS-002 CDM器件认证等级

| 认证等级 | 最大耐受测试条件     |

|------|--------------|

| C0a  | < 125        |

| C0b  | 125 to <250  |

| C1   | 250 to <500  |

| C2a  | 500 to <750  |

| C2b  | 750 to <1000 |

| C3   | ≥1000        |

表2.6 AEC-Q100-011 CDM器件认证等级

| 认证等级 | 最大耐受测试条件                                                    |

|------|-------------------------------------------------------------|

| C0a  | <tc 125<="" td=""></tc>                                     |

| C0b  | TC 125 to <tc 250<="" td=""></tc>                           |

| C1   | TC 250 to <tc 500<="" td=""></tc>                           |

| C2   | TC 500 to <tc 750<="" td=""></tc>                           |

| C2a  | TC 500 to <tc 750<br="">(with corner pins<br/>≥TC 750)</tc> |

| C2b  | TC 750 to <tc 1000<="" td=""></tc>                          |

| C3   | TC 1000                                                     |

在样品测试处理方面,AEC-Q100-011在测试前后均要求常温和高温电性测试,在电性PASS后才可认证芯片的CDM资格,而JS-002仅要求常温测试。在Zap次数上,CDM和HBM类似,AEC-100-011同样要求每个电压等级进行3次Zap,以提高CDM测试的稳定性。

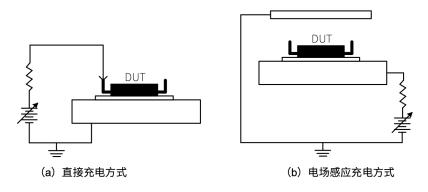

此外,在CDM测试方法上,JS-002和AEC-Q100-011均规定使用Non-Socket即电场感应式充电方法,如图2.1(b)所示, 在被测芯片上方放置一块金属接地平面,芯片下方的金属板被称为场板。场板的电位由高电压电源通过一个高阻值电阻进行控制。若场板与芯片之间的电容远大于芯片与接地平面之间的电容,则芯片的电位将与场板的电位紧密跟随。相较于图2.1(a)所示使用机械针直接对芯片充电的方法,电场感应充电方法模拟了芯片自身充放电的真实环境,更接近于真实工况。

图2.1 CDM测试充电方式示意图

总的来说,AEC-Q100-011对于CDM测试要求更为严格,在考虑特定工况下补充了测试条件,提高了测试和验证的可重复性,对于取得AEC-Q100-011要求CDM认证的芯片,足以具备通过JS-002测试的性能。

#### 2.3.Latch up测试标准及差异

Latch up国际通用标准为JESD78F.02和AEC-Q100-004-REVD。两者的主要差异如下表所示:

表2.7 JESD78F.02和AEC-Q100-004主要差异对比

| 对比项           | JESD78F.02    | AEC-Q100-004              |  |

|---------------|---------------|---------------------------|--|

| 信号引脚测试方法      | I-Test或E-Test | -Test或E-Test 要求使用E-test方法 |  |

| 样品测试处理        | 常温前后电性测试,高温可选 | 测试前和测试后进行常温&高温(125°C)测试   |  |

| 测试温度 正常工作温度测试 |               | 在最高环境工作温度下测试              |  |

如1.2节所述,Latch up测试分为电源PIN过压测试和信号PIN电流注入测试。JESD78F和AEC-Q100-004 中对于电源PIN过压测试要求相同,对于信号PIN电流注入测试,AEC-100-004规定使用E-test方法。如表2.8所示为I-test和E-test注入正极性电流的对比,两种方法均致力于向引脚注入电流,但以不同的脉冲触发形式施加。由于芯片对I-Test脉冲较为敏感,容易引发EOS类的失效,AEC-Q100-004中规定使用E-test方法对信号PIN进行电流注入测试,该方法能够在不引发EOS的前提下,对芯片的输入输出引脚进行评估。

表2.8 I-test和E-test方法对比(正极性)

| 触发方法   | 施加应力                   | 钳位设置                   | 备注       |

|--------|------------------------|------------------------|----------|

| 电流脉冲   | 施加测试等级下                | 钳位电压为                  | 若施加电压超出  |

| I-Test | 最大触发电流                 | Vimax+0.5(Vimax-Vimin) |          |

| 电压脉冲   | 施加测试等级最大电压             | 钳位电流为                  | MSV,则将施加 |

| E-Test | Vimax+0.5(Vimax-Vimin) | 测试等级下最大电流              | 电压设为MSV  |

值得注意的是,JESD78F和AEC-Q100-004中信号PIN电流注入测试均针对于输入信号引脚,芯片输出信号引脚无需进行电流注入测试。如表2.9所示为E-test的电压施加方法,输出引脚仅需在测试中保持最大输出工作电压,这是因为芯片输出引脚通常为强上拉或强下拉结构,在进行电流注入测试时会造成输出引脚短路。

表2.9 E-test引脚电压施加方法

| 测试方法   | 电压极性 | 输入PIN状态 | 输出PIN状态 | 输入PIN施加电压条件             | 备注                  |

|--------|------|---------|---------|-------------------------|---------------------|

| E-Test | 正极性  | Vimax   | Vomax   | Vimax+0.5 (Vimax-Vimin) | 若施加电压超出             |

| E-162f | 负极性  | Vimin   | Vomin   | Vimin-0.5 (Vimax-Vimin) | MSV,则将施加<br>电压设为MSV |

在测试条件上,AEC-Q100-004还要求在常温和最高环境温度下进行Latch up测试,并在测试前和测试后进行高温性能验证,相对于JESD78F.02增加了测试样本量和温度条件验证。因此,AEC-Q100-004对于Latch up的测试条件更为严格,并尽量避免了因EOS失效导致的测试工况,通过AEC-100-004测试的芯片可以满足JESD78F.02的测试要求。

此外,对于已经通过Latch up测试的芯片,部分测试机构支持继续对电源引脚施加大于Latch up标准(1.5倍最大工作电压)的电压,直至芯片因过电应力损伤,从而得到在Latch up电压脉冲条件下的 EOS电压,对于测试芯片的实际极限耐压能力具有一定参考作用。

### 3.总结

本文档介绍了HBM、CDM和Latch up测试的基本原理,分析了JEDEC和AEC-Q100标准的主要差异,AEC-Q100标准基于JEDEC等级,但在特定测试条件和性能验证上的要求相对严格。通过对标准的差异分析,说明了通过AEC资质认证的芯片具备通过JEDEC标准相同等级的能力。

#### 参考资料:

1.纳芯微电子,芯片级ESD与系统级ESD测试标准介绍和差异分析,AN-13-0009.

#### 4.修订历史

| 版本  | 描述     | 作者                        | 日期        |

|-----|--------|---------------------------|-----------|

| 1.0 | 创建应用笔记 | Shuo Zhang, Runsheng Zhou | 2025/9/20 |

销售联系方式: sales@novosns.com; 获取更多信息: www.novosns.com

### 重要声明

本文件中提供的信息不作为任何明示或暗示的担保或授权,包括但不限于对信息准确性、完整性,产品适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的陈述或保证。

客户应对其使用纳芯微的产品和应用自行负责,并确保应用的安全性。客户认可并同意:尽管任何应用的相关信息或支持仍可能由纳芯微提供,但将在产品及其产品应用中遵守纳芯微产品相关的所有法律、法规和相关要求。

本文件中提供的资源仅供经过技术培训的开发人员使用。纳芯微保留对所提供的产品和服务进行更正、修改、增强、改进或其他更改的权利。纳芯微仅授权客户将此资源用于开发所设计的整合了纳芯微产品的相关应用,不视为纳芯微以明示或暗示的方式授予任何知识产权许可。严禁为任何其他用途使用此资源,或对此资源进行未经授权的复制或展示。如因使用此资源而产生任何索赔、损害、成本、损失和债务等,纳芯微对此不承担任何责任。

有关应用、产品、技术的进一步信息,请与纳芯微电子联系( www.novosns.com )。

苏州纳芯微电子股份有限公司版权所有